# СЕКЦИЯ 2

## НАУКОЕМКИЕ ТЕХНОЛОГИИ

Председатель: профессор Парфенов Е.М.

Руководитель экспертной комиссии: профессор Белов Б.И.

Ученый секретарь: Соловьев В.А.

Экспертная комиссия: профессор ЧЕКАНОВ А.Н, к.т.н. БИЛИБИН К.И., к.т.н. БУРАК Б.А., к.т.н. ГРИГОРЬЕВ В.П., к.т.н. ГРИДНЕВ В.Н., к.т.н. ИВАНОВ Ю.В., к.т.н. МАРКЕЛОВ В. В., к.т.н. ПАРФЕНОВ О.Д., ГЛАЗУНОВА Г.П.

#### РАЗРАБОТКА РАСПИСАНИЯ ЗАПУСКА В ПРОИЗВОДСТВО ЭЛЕКТРОННЫХ ЯЧЕЕК ПРИ ОБЪЕМНОМ ПЛАНИРОВАНИИ

Иванов Юрий Викторович, Курносенко Алексей Евгеньевич каф. ИУ-4 МГТУ им. Н.Э. Баумана

Иу4, Московский государственный технический университет им. Н.Э. Баумана

# WORKING OUT THE TOTAL PLAN OF ELECTRONIC BOARDS PRODUCTION LAUNCHING

Ivanov Jury V., Kurnosenko Alexey E.

IU-4 department of BMSTU Ivanov Jury V.

IU4, Bauman Moscow State Technical University.

mario7@online.ru

#### Аннотация

Рассматривается метод разработки расписания запуска электронных ячеек на сборку в условиях гибкого автоматизированного многономенклатурного производства. Метод включает этапы объемного и календарного планирования. Описывается первый этап, на котором решается задача распределения годовой программы запуска по плановым периодам — месяцам и декадам с учетом ограничений на годовой (месячный) объем запуска в единицах продукции, загрузку оборудования и объем запуска в денежном выражении. Abstract

The method of working out the plan of launching the flexible automated production of electronic boards is discussed. The method contains of two main stages: total and calendar planning. On the first stage the problem of distribution of the year production program to months and decades is worked out. The limitations on the year (month) production program, equipment charging and on the total amount of production are taken into account.

Общая задача разработки расписания запуска электронных ячеек (ЭЯ) в условиях многономенклатурного производства представлена двумя взаимоувязанными этапами: объемного и календарного планирования.

Задачей первого этапа является разработка программ запуска ЭЯ в производство для гибкого автоматизированного сборочного комплекса (ГАСК) по плановым периодам (ПП) месяцам (ПП–М) и декадам (ПП–Д) с учетом следующих ограничений по каждому ПП:

- на максимальную и минимальную загрузку автоматизированного технологического оборудования (ATO);

- на максимальный и минимальный годовой (месячный) объем запуска в шт. ЭЯ;

- на минимальный объем запуска ЭЯ в денежном выражении (рублях).

Второй этап отвечает за разработку сменных и суточных программ запуска ЭЯ в производство с учетом следующих ограничений по каждому ПП:

- на декадный объем запуска ЭЯ;

- на максимальную продолжительность непрерывной сборки ЭЯ одного типа;

- на максимально допустимый объем переменных затрат производства в ГАСК.

#### Этап объемного планирования

Задача распределения годовой производственной программы по плановым периодам относится к классу задач объемного планирования и решается характерными для него методами линейного программирования (ЛП). Целесообразность применения методов ЛП для решения задачи объемного планирования показана в работах [2...5]. При этом существенным моментом является выбор конкретного метода решения задачи ЛП (ЗЛП).

Наиболее часто для решения ЗЛП в приведенной постановке задачи применяются различные версии метода последовательных улучшений [7,8]. По критерию обеспечения высокого быстродействия при решении задач с большим числом переменных и ограничений в сочетании с экономией ресурсов памяти ЭВМ на основе сравнения эффективности

процедур метода последовательных улучшений [5,7,8] для решения данной задачи был выбран метод обратной матрицы. За основу взята процедура «MSimplex» [5,8].

Чтобы сделать организационную структуру ГАСК более гибкой, указанные методы в условиях реального производства применялись с учетом дополнений [2]. Все ЭЯ условно подразделяются на две группы – регламентированную  $Y^{per}$  и нерегламентированную  $Y^{heper}$ . К первой относятся ЭЯ, по которым предприятие не может самостоятельно изменять объемы и сроки запуска по ПП-М (ПП-Д). Ко второй группе относятся остальные ЭЯ, по которым предприятию предоставлена возможность их распределения по срокам и объемам запуска. При этом решение задачи объемного планирования проводится в два этапа.

На этапе I—а осуществляется директивное распределение программы запуска ЭЯ регламентированной группы в производство, на этапе I—б применительно к ЭЯ нерегламентированной группы применен симплекс—метод. Этап I—a.

Расчет ведется для каждого m –го ПП–М и d –го ПП–Д в составе каждого ПП–М по всем операциям  $\{\widetilde{O}_z\}$  автоматизированного технологического процесса (АТП) сборки ЭЯ (кроме подготовительных операций).

Требуемые для выполнения регламентированной части программы запуска временные ресурсы (фонд времени ATO в составе ГАСК) на операции  $\widetilde{O}_z$  определяются по формуле:

$$T_{n zm}^{per.} = \sum_{i=1}^{N_a} \left( N_{\mathfrak{I}_{3m \, mi}} \cdot T_{mr \, iz} \right) \cdot K_{n-3} \tag{1},$$

где  $K_{\pi-3} = \frac{T_{\text{шт}} + T_{\pi-3}}{T_{\text{шт}}}$  — коэффициент затрат подготовительно—заключительного времени на операцию.

Располагаемые ресурсы операции  $\tilde{O}_{z}$  при  $K_{3} = 1$  определяются по формуле [6]:

$$T_{pzm} = N_{ob,z} \cdot F_{M.9\phi,zm} \cdot K_{THz} \cdot \rho_z$$

(2),

где  $N_{\text{об.z}}$ ,  $K_{\text{тп z}}$ ,  $\rho_z$  — соответственно количество единиц оборудования, коэффициент выхода годных и коэффициент готовности для ATO, назначенного на операцию  $\widetilde{O}_z$ .

Рассчитывается фактический коэффициент загрузки ATO на операции  $\widetilde{O}_z$  при выполнении регламентированной части программы:

$$K_{3,\phi,zm}^{\text{per.}} = \frac{T_{\pi\,zm}^{\text{per.}}}{T_{p\,zm}}$$

(3).

Ограничения на загрузку ATO в составе ГАСК для операции  $\widetilde{O}_z$  можно записать в виде системы двух неравенств:

$$\begin{cases} K_{3,\varphi,zm}^{per.} \leq K_{3,zm}^{max}; \\ K_{3,\varphi,zm}^{per.} \geq K_{3,zm}^{min} \end{cases} \tag{4}.$$

Сначала производится проверка отсутствия чрезмерной загрузки ATO на операции  $\widetilde{\mathrm{O}}_{\mathrm{z}}$ :

$$K_{3,\varphi,zm}^{per.} \le K_{3,zm}^{max} \tag{4a}.$$

Если условие (4a) не выполнено, дальнейший расчет становится невозможным. В противном случае проводится проверка попадания фактического коэффициента загрузки ATO на операции  $\tilde{\rm O}_z$  в допустимый диапазон:

$$K_{3,\phi,zm}^{\text{per.}} \ge K_{3,zm}^{\text{min}}$$

(46).

Если условие (4б) выполнено, то максимальное и минимальное значения требуемых временных ресурсов на выполнение нерегламентированной части программы запуска для ATO на операции  $\tilde{\rm O}_z$  приравниваются к 0:

$$T_{p\,zm}^{\,\text{Heper. max}} = 0; \ T_{p\,zm}^{\,\text{Heper. min}} = 0 \tag{5},$$

в противном случае они подлежат определению по формулам:

$$T_{p\,zm}^{\,\text{Heper,\,max}} = T_{p\,zm} \cdot K_{3.\,jm}^{\,\text{max}} - T_{\pi\,zm}^{\,\text{per.}}; \ T_{p\,zm}^{\,\text{Heper,\,min}} = T_{p\,zm} \cdot K_{3.\,jm}^{\,\text{min}} - T_{\pi\,zm}^{\,\text{per.}} \tag{6}.$$

Определяется также минимальное значение объема запуска ЭЯ в рублях:

$$C_{m}^{\text{Heper. min}} = C_{m}^{\text{min}} - \sum_{\substack{i=1\\i \in Y_{m}^{\text{per}}}}^{N_{a}} C_{i} \cdot N_{\mathfrak{I}_{M} \text{ mi}}$$

$$\tag{7}.$$

Этап І-б.

Задачей этапа является корректировка разработанной на этапе I—а программы запуска ЭЯ в производство для каждого ПП-М (ПП-Д) с учетом ЭЯ нерегламентированной группы. Решение проводится симплекс-методом обратной матрицы. Формализованная запись для ПП-М приведена ниже.

$$\begin{cases} F(N_{\kappa \, _{98 \, mi}}) = \sum_{m=1}^{12} \sum_{i=1}^{N_a} c_{mi} \cdot N_{\kappa \, _{98 \, mii}} \rightarrow max; c_{mi} = \begin{cases} 1 \ \text{при} \ i \in Y_m^{\text{Heper}}; \\ 0 \ \text{при} \ i \in Y_m^{\text{Per}}. \end{cases} \end{cases} \begin{cases} \sum_{i=1}^{N_a} a_{mi,k} \cdot N_{\kappa \, _{98 \, mii}} \leq b_k; a_{mi,k} = \begin{cases} T_{mr \, iz} \cdot K_{n-3} \ \text{при} \ i \in Y_m^{\text{per}}; \\ 0 \ \text{при} \ i \in Y_m^{\text{per}}. \end{cases} \end{cases} \\ \begin{cases} \sum_{i=1}^{N_a} a_{mi,k} \cdot N_{\kappa \, _{98 \, mii}} \geq b_k; a_{mi,k} = \begin{cases} T_{mr \, iz} \cdot K_{n-3} \ \text{при} \ i \in Y_m^{\text{per}}; \\ 0 \ \text{при} \ i \in Y_m^{\text{per}}; \end{cases} \end{cases} \end{cases} \\ \begin{cases} \sum_{i=1}^{N_a} a_{mi,k} \cdot N_{\kappa \, _{98 \, mii}} \geq b_k; a_{mi,k} = \begin{cases} C_i \ \text{при} \ i \in Y_m^{\text{Heper}}; \\ 0 \ \text{при} \ i \in Y_m^{\text{per}}; \end{cases} \end{cases} \\ \begin{cases} b_k = \left[ \frac{T_{pzm}^{\text{Heper, min}}}{N_{nn \, \kappa}} \right]; k = \overline{12 \cdot |z|} + 1,2 \cdot 12 \cdot |z| \end{cases} \end{cases} \end{cases} \\ \begin{cases} \sum_{i=1}^{12} a_{mi,k} \cdot N_{\kappa \, _{98 \, mii}} \geq b_k; a_{mi,k} = \begin{cases} C_i \ \text{при} \ i \in Y_m^{\text{Heper}}; \\ 0 \ \text{при} \ i \in Y_m^{\text{per}}; \end{cases} \end{cases} \end{cases} \end{cases} \\ \begin{cases} b_k = \left[ \frac{C_m^{\text{Heper, min}}}{N_{nn \, \kappa}} \right]; k = \overline{2 \cdot 12 \cdot |z|} + 1,2 \cdot 12 \cdot |z| + 12 \cdot N_a \end{cases} \end{cases} \end{cases} \end{cases} \end{cases}$$

где:  $N_{_{98\ mi}}$  — искомые программы запуска ЭЯ в производство по ПП–М; |Z| — количество технологических операций в составе АТП, за исключением подготовительных;  $Y_{m}^{\text{нереr}}\left(Y_{m}^{\text{per}}\right)$  — множество индексов типов ЭЯ, входящих в нерегламентированную (регламентированную) группу в данном ПП–М;  $N_{98\ i}^{min}\left(N_{98\ i}^{max}\right)$  — минимально (максимально) допустимый годовой объем запуска ЭЯ i —го типа за вычетом регламентированной части программы запуска;  $N_{\kappa\,98\,mi}$  — программа запуска в производство ЭЯ i —го типа в m —ом ПП–М, выраженная в партиях ЭЯ (ориентация идет на сборку партии ЭЯ, равной транспортной партии);  $N_{nn\,\kappa}$  — количество ЭЯ в транспортной партии;  $N_{98\,mi}$  =  $N_{\kappa\,98\,mi}$  ·  $N_{nn\,\kappa}$  .

#### Пример

На сборку запускаются ЭЯ пяти различных типов на базе ИС в корпусе 201, а также ЭРЭ с радиальными и осевыми выводами.  $N_{39i}^{HOM}=10000$ ,  $N_{39i}^{max}=10500$ ,  $N_{39i}^{min}=9500$  [ЭЯ/год],  $C_i=300$  [руб.]. В качестве АТО для монтажа ЭК всех указанных типов используется сборочный центр. Для каждого ПП-М: Д=24,  $C_m=90000$  [руб.],  $C_m^{min}=80000$  [руб.],  $F_{\text{м.эф. zm}}=420$  [Ч.],  $K_{3.\text{zm}}^{\text{треб.}}=0.8; \Delta K_{3.\text{zm}}^+=\Delta K_{3.\text{zm}}^-=0.05$ . Для каждого ПП-Д в составе ПП-М: Z=8, Z=

Таблица 1. Результаты этапа I – программы запуска ЭЯ в производство для ПП-М и ПП-Д

| Месяцы  | Декада 1, №ЭЯ   | Декада 2 №ЭЯ,    | Декада 3 №ЭЯ, | Месяц, №ЭЯ       |

|---------|-----------------|------------------|---------------|------------------|

|         | [шт.]           | [шт.]            | [шт.]         | [шт.]            |

| Январь  | 3[4860]         | 3[1440], 4[1840] | 4[2220]       | 3[6000], 4[3860] |

| Февраль | 4[2260]         | 4[2500]          | 4[2220]       | 4[6640]          |

| Март    | 2[60], 3[4720]  | 2[2480]          | 2[2200]       | 2[4520], 3[4500] |

| Апрель  | 1[740], 2[1580] | 2[2480]          | 2[2200]       | 1[700], 2[5980]  |

| Май     | 1[2520]         | 1[2800]          | 1[2480]       | 1[7440]          |

| Июнь     | 1[2480], 5[20] | 5[2120] | 5[1880] | 1[2360], 5[3840] |

|----------|----------------|---------|---------|------------------|

| Июль     | 5[1880]        | 5[1880] | 5[1820] | 5[5320]          |

| Август   | 5[100]         | 5[80]   | 5[80]   | 5[260]           |

| Сентябрь | 5[100]         | 5[80]   | 5[80]   | 5[260]           |

| Октябрь  | 5[100]         | 5[80]   | 5[80]   | 5[260]           |

| Ноябрь   | 5[100]         | 5[80]   | 5[80]   | 5[260]           |

| Декабрь  | 5[100]         | 5[80]   | 5[80]   | 5[260]           |

В ПП-М «Январь»÷ «Июнь» для монтажного ATO К<sub>3</sub> = 0,88; для остального ATO в составе ГАСК  $K_2 = 0.1 \div 0.2$ , при этом объем запуска ЭЯ в рублях составляет  $C = 1860 \div 2958$ [тыс. руб./месяц]. Из системы ограничений (8) удалось выполнить все, кроме ограничения на загрузку АТО снизу для всех операций, кроме монтажной, т.е. при обеспечении необходимой загрузки монтажного ATO остальное технологическое оборудование вынуждено простаивать в большей степени, нежели это было допущено в исходных данных. Такая ситуация является типичной, так как лимитирующей по длительности операцией в ГАСК в подавляющем большинстве случаев является монтажная. Учитывая максимальную концентрацию разнотипных переходов на данном монтажном рабочем месте, эта ситуация в нашем случае проявляется наиболее выпукло. Для ПП-М «Июль» ÷ «Декабрь» заданной годовой программы запуска не хватило для обеспечения адекватной загрузки АТО, поэтому коэффициент загрузки для всех без исключения операций в ГАСК не превышает 4%. При этом объем запуска ЭЯ в рублях составляет С = 80 [тыс. руб./месяц], что соответствует заданному минимальному значению. Суммарная программа запуска по всем ПП-М находится в допустимых пределах относительно заданной годовой программы (±5%), то же самое относится к суммарной программе запуска по всем ПП-Д относительно месячной программы.

Таким образом, на основании результатов этапа I можно сделать следующие выводы:

- выполнено деление ЭЯ на регламентированную и нерегламентированную группы;

- разработаны месячные и декадные программы запуска ЭЯ в производство по всем ПП-М и ПП-Д, полностью удовлетворяющие ограничениям на максимальный и минимальный годовой (месячный) объем запуска;

- полностью выполнены ограничения на максимальную загрузку АТО;

- ограничения на минимальную загрузку ATO выполнены только для монтажного оборудования в некоторых ПП;

- полностью выполнены ограничения на минимальный объем запуска ЭЯ в денежном выражении;

- подготовлены данные для проведения этапа II календарного планирования.

При увеличении задаваемой годовой номенклатуры и программы запуска ЭЯ можно ожидать полного удовлетворения всех ограничений, поставленных на рассматриваемом этапе.

Решить задачу данного этапа ручным директивным распределением годовой программы запуска не представляется возможным даже при небольшой номенклатуре и программе запуска ЭЯ из—за значительной трудоемкости проводимых расчетов. Литература

- 1. Петров В. А., Масленников А. Н., Осипов Л. А. Планирование гибких производственных систем. Л.: Машиностроение, 1985. 182 с.: ил.

- 2. Организация, планирование приборостроительного производства и управление предприятием: Учебник для студентов приборостроительных специальностей вузов /В. А. Петров, Л. П. Беликова, Э. В. Минько и др.; под общ. ред. В. А. Петрова. Л.: Машиностроение, 1987. 424 с.: ил.

- 3. Шкурба В. В. и др. Планирование и управление в автоматизированном производстве. Киев, Наукова думка, 1985.

- 4. Семенов А. И., Португал В. М. Задачи теории расписаний в календарном планировании мелкосерийного производства. М.: Машиностроение, 1972.

- 5. Первозванский А. А. Математические модели в управлении производством. М.: Наука, 1975 616 с.: ил.

- 6. Иванов Ю. В. Повышение эффективности сборки изделий. М.: Вестник МГТУ, №4,1995, с. 66-75.

- 7. Романовский И. В. Алгоритмы решения экстремальных задач. М.: Наука, 1975.

- 8. Грибов А. Б., Романовский И. В. Программирование симплекс–метода и его вариантов на Алголе. В сб. «Оптимальное планирование», №12. Новосибирск: Наука, 1969.

## РАЗРАБОТКА И ОПТИМИЗАЦИЯ РАСПИСАНИЯ ЗАПУСКА В ПРОИЗВОДСТВО ЭЛЕКТРОННЫХ ЯЧЕЕК ПРИ КАЛЕНДАРНОМ ПЛАНИРОВАНИИ

Иванов Юрий Викторович, Курносенко Алексей Евгеньевич *к.т.н., доц. каф. ИУ–4 МГТУ им. Н.Э. Баумана Иванов Юрий Викторович* Иу4, Московский государственный технический университет им. Н.Э. Баумана

#### WORKING OUT THE CALENDAR PLAN OF ELECTRONIC BOARDS PRODUCTION LAUNCHING

Ivanov Jury V., Kurnosenko Alexey E.

candidate of tech. science, assistant professor, IU–4 department of BMSTU Ivanov Jury V.

Iu4, Bauman Moscow State Technical University.

mario7@online.ru

#### Аннотация

В статье рассматривается метод разработки расписания запуска электронных ячеек на сборку в условиях гибкого автоматизированного многономенклатурного производства. Метод включает этапы объемного и календарного планирования. Описывается второй этап, на котором решается задача разработки сменных и суточных заданий. Определяется оптимальная последовательность сборки электронных ячеек. Учитываются ограничения на декадный объем запуска электронных ячеек, продолжительность непрерывной сборки электронных ячеек одного типа, а также на объем переменных затрат производства по каждому плановому периоду.

#### Abstract

The method of working out the plan of launching the flexible automated production of electronic boards is discussed. The method contains of two main stages: total and calendar planning. On the second stage the problem of making shift and day production programs is worked out. Optimum sequence of electronic board assembling is defined. Time limitations on decade production program, uninterrupted assembling of electronic boards of the same type and limitations on the production expenses in each planning period are taken into account.

На первом этапе [см. статью Иванова Ю.В. и Курносенко А.Е. «Разработка расписания запуска в производство электронных ячеек (этап объемного планирования»)] решалась задача разработки программ запуска электронных ячеек (ЭЯ) в производство для гибкого автоматизированного сборочного комплекса (ГАСК) по плановым периодам (ПП) месяцам (ПП-М) и декадам (ПП-Д) с учетом следующих ограничений по каждому ПП:

- на максимальную и минимальную загрузку автоматизированного технологического оборудования (ATO);

- на максимальный и минимальный годовой (месячный) объем запуска в шт. ЭЯ;

- на минимальный объем запуска ЭЯ в денежном выражении (рублях).

#### Этап календарного планирования

Задача этапа сводится к разработке сменно–суточных заданий, реализующих задания и сроки на основе результатов первого этапа планирования с учетом следующих ограничений по каждому  $\Pi\Pi$ :

- на декадный объем запуска ЭЯ;

- на максимальную продолжительность непрерывной сборки ЭЯ одного типа;

- на максимально допустимый объем переменных затрат производства в ГАСК.

Особенности постановки задачи календарного планирования для ГАСК сборки ЭЯ в условиях многономенклатурного производства с учетом указанных ограничений не позволяют в полной мере использовать для ее решения методы, описанные в литературе по машиностроительному производству, поэтому потребовалась разработка метода,

позволяющего учесть данную специфику. Решение задачи календарного планирования разработанным методом проводится в два рассмотренных ниже этапа. Этап II-a.

Задачей данного этапа является определение оптимальной последовательности сборки ЭЯ из заданной номенклатуры по всем ПП–Д в составе каждого ПП–М.

Оптимальная последовательность сборки ЭЯ соответствует минимуму суммарного времени, затрачиваемого на переналадку АТО при сборке ЭЯ в данной последовательности. Рассчитывается суммарное время переналадок монтажного АТО  $T_{\text{пер}\Sigma}$  и решается задача оптимизации последовательности переналадок АТО при сборке ЭЯ декадной номенклатуры по критерию  $T_{\text{пер}\Sigma} \to \min$ , которую можно сформулировать в виде задачи о назначениях [2]:

$$\sum_{i=1}^{n_{md}}\sum_{j=1}^{n_{md}}t_{ij}x_{ij} \rightarrow \min \ \pi pu \ \begin{cases} \sum_{j=1}^{n_{md}}x_{ij} = 1; \sum_{i=1}^{n_{md}}x_{ij} = 1; \sum_{i=1}^{k}x_{ij}^{(k)} = 1; \sum_{j=1}^{k}x_{ij}^{(k)} = 1; j = 1, 2, \dots, n_{md}; x_{ij} = 0, 1 \forall i, j. \end{cases} \tag{1}$$

где:  $n_{md}$  – количество типов ЭЯ в декадной программе d –го ПП–Д  $\,$  m –го ПП–М;

$T = \left\| t_{ij} \right\|_{n_{md} \times n_{md}} - \text{матрица переналадок ATO со сборки ЭЯ типа } i \text{ на сборку ЭЯ типа } j;$

$t_{ij} = t_{nep\ ij} = T_{cnp\ ij} + T_{ccr\ ij} + T_{cduah\ ij} + T_{chn\ ij}$  — время переналадки АТО [4] со сборки ЭЯ типа і на сборку ЭЯ типа ј; включает время смены/наладки приспособления для установки и точной фиксации ПП  $T_{cnp\ ij}$ , сборочной головки или их комплекта  $T_{ccr\ ij}$ , базовой части накопителя ЭК  $T_{cduah\ ij}$ , носителя программ  $T_{chn\ ij}$ .

$$X = \left\| x_{ij} \right\|_{n_{md} \times n_{md}} - \text{матрица, в которой}$$

$$x_{ij} = \begin{cases} 1, \text{если в маршрут входит переналадка от ЭЯ типа і к ЭЯ типа j;} \\ 0 \text{ в противном случае.} \end{cases} \tag{2}.$$

Решение задачи заключается в преобразовании матрицы X от начального состояния, заданного неоптимальной последовательностью переналадок, в конечное состояние, определяемое системой (1). Применяемый метод решения – метод многоугольника [3].

В результате решения задачи получаем последовательность индексов собираемых ЭЯ  $l_1, l_2, \dots, l_{n_{md}} \left(l_k \in \left\{\overline{l, n_{md}}\right\}, l_i \neq l_j \forall l_i, l_j \in \left\{\overline{l, n_{md}}\right\}$  такую, что  $t_{l_1 l_2 +} t_{l_2 l_3} + \dots + t_{l_{n_{md} - l} l_{n_{md}}} + t_{l_{n_{md}} l_1} \rightarrow \min$  (3). Этам ІІ—б.

Задачей данного этапа является разработка собственно сменно-суточных заданий, т.е. определение программ запуска ЭЯ в производство на ПП – сутки (рабочие смены), входящие в состав каждого планируемого d –го ПП–Д в составе m –го ПП–М. Математическая формулировка задачи для ПП – рабочей смены:

определить множество сменных программ запуска ЭЯ в производство

$${N_{\text{эя mdysi}}}$$

$\forall i = \overline{1, n_{\text{md}}}$  при условии

$$\begin{cases} T_{\kappa,c\delta,\ i} - T_{\mu,c\delta,\ i} \leq \left[ T_{\text{henp,c\delta},\ i} \right] \forall i = \overline{1,n_{\text{md}}}; \\ C_{y\,\text{on}\Sigma} \leq \left[ C_{y\,\text{on}\Sigma} \right] \forall y \in D \text{ либо } C_{s\,\text{on}\Sigma} \leq \left[ C_{s\,\text{on}\Sigma} \right] \forall s \in y, y \in D; \\ \sum_{s\,y} N_{\,\text{sg mdysi}} = \left[ N_{\,\text{sg mdi}} \right] \forall i = \overline{1,n_{\text{md}}}, s \in y, y \in D \end{cases} \tag{5}$$

где:  $T_{\text{н.сб. i}} (T_{\text{к.сб. i}})$  – время начала (окончания) сборки партии ЭЯ і –го типа;

$\left[T_{\text{непр.сб. i}}\right]$  — максимальная длительность непрерывной сборки партии ЭЯ і –го типа;

$N_{_{\text{эм mdysi}}}$  – программа запуска в производство ЭЯ  $\,$  i –го типа на смену  $\,$  s рабочего дня  $\,$  у ;

$[N_{99 \text{ mdi}}]$  — декадная программа запуска в производство ЭЯ і—го типа в d—ом ПП—Д в составе m—го ПП—М, разработанная на I—ом этапе; s — номер смены в составе рабочего дня; у — номер рабочего дня в составе декады; D — множество рабочих дней в составе декады;

$C_{son\Sigma}$  ( $C_{yon\Sigma}$ ) [переменные затраты на производство данного сменного (суточного) задания в ГАСК] вычисляются в соответствии с методикой [4,5], при этом

$$C_{son\Sigma} = \sum_{z=1}^{|Z|} C_{son} \left( \widetilde{O}_{z} \right); C_{yon\Sigma} = \sum_{k=1}^{n_{cM}} C_{son\Sigma k}$$

(8),

где: |Z| — количество технологических операций в составе автоматизированного технологического процесса (АТП), за исключением подготовительных;  $n_{cm}$  — количество рабочих смен в рабочем дне при производстве в ГАСК.

Для решения задачи в данной постановке был разработан метод, который можно условно назвать методом поэтапных расчетов и согласований.

Суть метода заключается в последовательном заполнении ПП – смен и суток, начиная с первого. При этом очередь ЭЯ, кандидатов на запуск в каждом ПП (смене), соответствует оптимальной последовательности переналадок (3), полученная на этапе II—а. При каждом запуске нового типа ЭЯ в производство определяется ее программа запуска на данный ПП (порядок определения см. ниже) при условии выполнения ограничения (5). Если ограничение выполнено, ЭЯ запускается в производство в данном ПП, если нет — временно отвергается, но остается в очереди. Производится переход к ЭЯ следующего типа в последовательности (3). Ограничение (5) может не выполняться, если количество ЭЯ в очереди недостаточно для осуществления чередования сборки ЭЯ различных типов с одновременным выполнением ограничения (7) для всех типов ЭЯ. ЭЯ удаляется из очереди в случае выполнения для нее ограничения (7). Ограничения (6) проверяются после заполнения каждого ПП, по которому осуществляется контроль объема переменных затрат. В случае невыполнения условий (6) программа запуска для данного ПП последовательно уменьшатся до момента выполнения условий. При этом возможен возврат в очередь некоторых типов ЭЯ, ранее удаленных из нее в данном ПП.

Выше было сказано, что при каждом запуске ЭЯ в ПП — рабочей смене определяется ее программа запуска  $N_{\rm эя\ mdysi}$ . Под данной процедурой подразумевается определение оптимального размера партии запуска ЭЯ данного типа. Для решения данной задачи был выбран критерий минимальной суммы квадратов отклонений времени сборки партии ЭЯ от фонда времени АТО в выбранном ПП [1]. Так как размер данной партии должен быть кратен размеру транспортной партии (ориентация идет на сборку партии ЭЯ, равной транспортной партии), запишем искомый размер партии  $N_{\rm эя\ mdysi}$  в виде  $N_{\rm эя\ mdysi}$  =  $K_{\rm тр.\ эя\ mdysi} \cdot N_{\rm пп\ к}$ , и в дальнейшем будем искать значение  $K_{\rm тр.\ эя\ mdysi}$  ( $N_{\rm пп\ k}$  — количество ЭЯ в транспортной партии).

Функция суммы квадратов отклонений запишется в этом случае в следующем виде:

$$F_{i} = \sum_{z=1}^{|Z|} (K_{Tp. 98 \text{ mdysi}} \cdot T_{iz} - L_{z \text{ mdys}})^{2}$$

(9)

где: z — индекс операций  $\widetilde{O}_z$  в составе АТП сборки ЭЯ;  $T_{iz} = T_{iii} + t_{nep \ l_i, l_{i-1}}$  — время сборки транспортной партии ЭЯ типа і с учетом времени переналадки АТО  $t_{nep \ l_i, l_{i-1}}$ ;

$L_{z \text{ mdys}} = F_{\text{пп.эф. zmd}} \cdot N_{\text{of } z} \cdot \kappa_{\text{3.zmd}}^{\text{тpe6.}} \cdot K_{\text{тп } z} \cdot \rho_{z}$  — сменный фонд времени группы ATO с учетом требуемого декадного коэффициента загрузки  $\kappa_{\text{3.zmd}}^{\text{тpe6.}}$  на операции  $\widetilde{O}_{z}$  [4].

Дифференцируя  $F_i$  по  $K_{\text{тр. эя isy}}$  и приравнивая производную к 0, получим:

$$\frac{dF_{i}}{dK_{\text{Tp. 3M mdysi}}} = 2\sum_{z=1}^{|Z|} \left(K_{\text{Tp. 3M mdysi}} T_{iz} - L_{z \text{ mdys}}\right) \cdot T_{iz} = 0$$

(10).

$$K_{\text{Tp. }98 \text{ mdysi}} = \left[ \sum_{z=1}^{|Z|} L_{z \text{ mdys}} \cdot T_{iz} / \sum_{z=1}^{|Z|} T_{iz}^{2} \right]$$

(11).

#### Пример

На сборку запускаются ЭЯ пяти различных типов на базе ИС в корпусе 201, а также ЭРЭ с радиальными и осевыми выводами.  $N_{99i}^{HOM} = 10000$ ,  $N_{99i}^{max} = 10500$ ,  $N_{99i}^{min} = 9500$  [ЭЯ/год],  $C_i = 300$  [руб.]. В качестве АТО для монтажа ЭК всех указанных типов используется сборочный центр. Для каждого ПП–М: Д = 24,  $C_m = 90000$  [руб.],  $C_m^{min} = 80000$  [руб.],  $F_{M.9d.\ zm} = 420$  [ч.],

$K_{3,zm}^{\text{треб.}} = 0.8; \Delta K_{3,zm}^{+} = \Delta K_{3,zm}^{-} = 0.05$ . Для каждого ПП-Д в составе ПП-М: Д = 8 ,  $C_{\text{md}} = 30000$  [руб.],  $C_{\text{md}}^{\text{min}} = 27000$  [руб.],  $F_{\text{м.эф. zmd}} = 140$  [ч.]. Для каждого ПП-рабочего дня в составе ПП-Д  $F_{\text{м.эф. zmd}} = 17.5$  [ч.]. Для каждого ПП-рабочей смены в составе ПП- рабочего дня  $F_{\text{м.эф. zmd}} = 7$  [ч.] (для смен 1,2),  $F_{\text{м.эф. zmd}} = 3.5$  [ч.] (для смены 3). Результаты этапа II сведены в таблицы 1 и 2. В связи с большим объемом результатов приведем наиболее характерные из них — для 2—ой декады января в таблице 1 и для 3—го рабочего дня этой декады по сменам в таблице 2).

Таблица 1. Результаты этапа II (декада). (рабочий день).

| Рабочи | R€⁰K   | $C_{y \text{ on}\Sigma}$ , | в %     | К <sub>нез. у</sub> |

|--------|--------|----------------------------|---------|---------------------|

| е дни  | [шт.]  | [руб.]                     | отн.    | οπΣ,                |

|        |        |                            | $[C_y]$ | [руб.]              |

|        |        |                            | οπΣ]    |                     |

| 1      | 3[700  | 48717.                     | 97,4    | 2211.1              |

|        | ]      | 3                          |         |                     |

|        |        |                            |         |                     |

| 2      | 3[700  | 48717.                     | 97,4    | 2211.1              |

|        | ]      | 3                          |         |                     |

| 3      | 3[40], | 43061.                     | 86,1    | 1267.2              |

|        | 4[320  | 5                          |         |                     |

|        | ]      |                            |         |                     |

| 4      | 4[340  | 42655.                     | 85,3    | 1209.8              |

|        | ]      | 8                          |         |                     |

| 5      | 4[340  | 42655.                     | 85,3    | 1209.8              |

|        | ]      | 8                          |         |                     |

| 6      | 4[340  | 42655.                     | 85,3    | 1209.8              |

|        | ]_     | 8                          |         |                     |

| 7      | 4[340  | 42655.                     | 85,3    | 1209.8              |

|        | ]      | 8                          |         |                     |

| 8      | 4[160  | 18132.                     | 36,2    | 540.0               |

|        |        | 3                          |         |                     |

Таблица 2. Результаты этапа II

| Рабочи<br>е<br>смены | RЄ <b>≪</b><br>[.тш] | C <sub>y οπΣ</sub> ,<br>[pyб.] | Κ <sub>нез. у</sub><br>οπΣ,<br>[руб.] |

|----------------------|----------------------|--------------------------------|---------------------------------------|

| 1                    | 3[40],<br>4[120      | 16240.<br>8                    | 529.3                                 |

| 2                    | 4[140<br>]           | 15835.<br>0                    | 472.0                                 |

| 3                    | 4[60]                | 10985.<br>8                    | 265.8                                 |

По приведенным результатам можно сделать следующие выводы:

- декадная программа, определенная на этапе I, выполнена полностью;

- ограничения на допустимый объем переменных затрат сборки ЭЯ по каждому рабочему дню выполнены, при этом уровень затрат в 7 днях из 8 не опускается ниже 85% от максимально допустимого значения, что приемлемо. Это стало возможным изза достаточной загрузки монтажного АТО в данном ПП–Д (88%);

- ограничение на минимальную допустимую продолжительность сборки ЭЯ одного типа выполнить не удалось: ЭЯ №3 собирается в течение 3–х рабочих дней, ЭЯ №4 в течение 6–ти. Невыполнение данного условия связано с ограниченной номенклатурой ЭЯ в программе запуска данной декады (всего 2 типа ЭЯ), но его можно выполнить при увеличении задаваемой годовой номенклатуры и программы запуска ЭЯ.

Ручное директивное распределение декадной программы запуска, в отличие от автоматизированного, отличалось значительной трудоемкостью проводимых расчетов и, кроме того, не позволило выполнить ограничения на допустимый объем переменных затрат сборки ЭЯ по рабочим дням N = 1 и 2 для рассмотренной выше 2—ой декады января (см. таблицу 3).

Таблица 3.Результаты этапа II – ручное распределение декадной программы запуска (рабочие дни №1,2)

| Рабочи №ЭЯ | $C_{y \text{ on } \Sigma}$ , | в % | К <sub>нез. у</sub> |

|------------|------------------------------|-----|---------------------|

|------------|------------------------------|-----|---------------------|

| е дни | [шт.] | [руб.] | отн.    | οπΣ,   |

|-------|-------|--------|---------|--------|

|       |       |        | $[C_y]$ | [руб.] |

|       |       |        | οπΣ]    |        |

| 1     | 3[800 | 59325. | 118,7   | 2576.0 |

|       | ]     | 0      |         |        |

| 2     | 3[640 | 53320. | 106,6   | 2257.7 |

|       | ]     | 0      |         |        |

|       | 4[60] |        |         |        |

#### Литература

- 9. Основы автоматизации управления производством/ Макаров И. М., Евтихеев Н. Н., Дмитриева Н. Д. и др./ Под ред. Макарова И. М. М.: Высшая школа, 1983 504 с.: ил.

- 10. Деньдобренько Б. Н., Малика А. С. Автоматизация конструирования РЭА: Учебник для вузов. М.: Высш. школа, 1980. 384 с.: ил.

- 11. Сигал И. Х. Комбинированные алгоритмы решения задачи коммивояжера. М.: Вычислительный центр АН СССР, 1985. 48 с.

- 12. Иванов Ю. В. Повышение эффективности сборки изделий. М.: Вестник МГТУ, №4,1995, с. 66-75.

- 13. Иванов Ю. В. Методика автоматизированного выбора структур ГАСК по обобщенному критерию. М.: МГТУ, 1999. 65 с.: ил.

#### ПРЕДОБРАБОТКА РУКОПИСНОГО ТЕКСТА, ВВЕДЕННОГО С БУМАЖНОГО НОСИТЕЛЯ, ПРИ РАСПОЗНАВАНИИ

#### Цыганков Ю.В.

**Научный руководитель профессор, д.т.н., заведующий кафедры ВТ ТПУ Марков Н.Г.**Томский политехнический университет, Томск, Россия

# PRECONDITIONING OF HANDWRITING TEXT, ACQUIRED FROM PAPER, IN RECOGNITION PROCESS

Tsygankov Y.V.

Instructor Prof. Nikolay G. Markov, Dr. Tech. Sci. Head of Computer Engineering

Department

Tomsk Polytechnic University, Tomsk, Russia Mail: tyv@ce.cctpu.edu.ru

#### Аннотация

Предлагается конечное принятие решения о классификации рукописных символов, введенных с бумажного документа, производить по дорабатываемому, в процессе принятия решения, растровому оригиналу этого символа. Весь процесс распознавания разделяется на четыре этапа: сегментация, выделение образа, предварительная обработка образа символа и конечная классификация. Описанная предварительная обработка символа, не имеет деструктивного свойства, т.е. после преобразования все линии имеют толщину в один элемент; преобразование не нарушает топологию символа (линиям и узлам исходного изображения соответствуют линии и узлы в преобразованном изображении); преобразование не нарушает основных размеров символа.

#### Abstract

The final decisionmaking about a classification of hand-written character, which entered from the paper document, is offered to make on variable raster of this character, during decisionmaking. The process of recognition is divided into four stages: segmentation, selection of an image, preprocessing of character image and final classification. The preprocessing of character, has no destruction, i.e. after transformation all lines have a thickness in one element; the transformation does not disturb topology of character (lines and to knots of an initial image there meet lines and knots in a transformed image); the transformation does not disturb main sizes of character.

В последнее время уровень бумажного документооборота значительно снизился, все большее количество организаций предпочитает электронную обработку информации. В то же время существует множество учреждений, в которых поступление информации извне затруднено без участия бумажных документов. Эта проблема особо актуальна в банках, налоговых инспекциях и других подобных учреждениях. В связи с этим обострилась проблема автоматического ввода и распознавания рукописной информации с бумажных документов.

В настоящее время технически не сложно преобразовать бумажный документ в цифровой растровый вид. Для этого производится множество разнообразных сканеров, цифровых фото и видео камер. Дальнейшее развитие исследований в этой области направлено лишь на нахождение способов более качественной передачи цветов и точной передачи деталей. Правда, еще не до конца решена проблема интеграции этих устройств с программными продуктами.

Если ввод бумажных документов в цифровой растровый вид можно считать решенной проблемой, то распознавание введенного документа все еще остается актуальной задачей. Хотя и созданы программы распознавания печатных документов с приемлемым качеством распознавания текста высокого и среднего качества, большинство разработанных систем дают большие погрешности при обработке текста низкого качества или текста с разной степенью яркости. Если же говорить о распознавании рукописного текста, то можно сказать, что результатов, удовлетворяющих практику, нам не известно.

Подавляющее большинство теорий распознавания символов направлены на выделение признаков из исходного образа, принимая любую предварительную обработку как нечто деструктивное. Те теории, которые используют предобработку, проводят лишь внешние, косметические преобразования. Мы же считаем, что конечное принятие решения о классификации символа эффективнее производить по дорабатываемому в процессе принятия решения растровому оригиналу этого символа.

Весь процесс распознавания разделим на четыре этапа: сегментация, выделение образа, предварительная обработка образа символа и конечная классификация.

Сегментация изображения документа это выделение на введенном документе той области, в которой представлен текст, отделение текстовой информации от графической. Многие системы распознавания печатного текста позволяют вручную сегментировать оригинал, т.к. автоматическая сегментация часто не дает положительных результатов. Например, рассматривают некоторые рисунки как текст, и текст, сильно подверженный искажению, как рисунок. Выделение образа представляет собой процесс разделения слитно написанного текста, на отдельные символы. А результатом предварительной обработки образа символа должен являться некоторый набор признаков, необходимый для дальнейшего принятия решения об идентификации символа.

Все три описанных выше процесса не могут быть разделены. Несмотря на видимое разделение, в каждый отдельный момент времени ведется обработка по всем трем направлениям в сочетании с процессом распознавания. Сегментация необходима, как правило, для минимизации вычислительного процесса, но эта задача до сих пор не решена. Введение критериев разделения текста и рисунка невозможно, а значит, необходимо каждый подвергать процессу распознавания И лишь неудовлетворительных результатах, делать выводы о наличии рисунка. После выделения образа необходимо произвести фильтрацию изображения. Аддитивный шум проявляется на изображении как разрозненные изменения изолированных элементов, не обладающие пространственной корреляцией. Искаженные элементы часто весьма заметно отличаются от соседних элементов. Это наблюдение послужило основой для многих алгоритмов. обеспечивающих подавление шума [1-5]. Поскольку шум пространственно декоррелирован, в его спектре, как правило, содержатся более высокие пространственные частоты, чем в спектре обычного изображения. Следовательно, низкочастотная фильтрация может служить эффективным средством сглаживания шумов. Нами были исследованы многие фильтрующие алгоритмы. В результате проделанных опытных работ получилось, что использование любого из методов в чистом виде невозможно, т.к. фильтрация приводит к размыванию границ символов, а часто к стиранию отдельных, значимых, элементов. Для устранения нежелательных последствий необходим постоянный контроль результатов фильтрации, а также предварительное исследование образа, на предмет предположительных размеров символов и толщины «стенки» символа. Исследования привели к тому, что наиболее удобным и простым в реализации оказался высокочастотный фильтр[5].

Массив Q размера M x M выходного изображения формируется путем дискретной свертки массива F размера N x N исходного изображения со сглаживающим массивом H размера L x L согласно формуле:

$$Q(m1,m2) = \sum_{n1} \sum_{n2} F(n1,n2)H(m1-n1+1,m2-n2+1).$$

Как уже нами отмечалось классификацию целесообразно производить по дорабатываемому образу, а значит далее необходимо произвести выделение образа, предварительную обработку образа и затем выделение признаков для последующей классификации. Используемое нами признаковое пространство и алгоритм классификации символов требует представление образа в несколько идеализированном виде. Для этого необходимо применить следующие преобразования.

Утоньшение «стенок» символа и заполнение пустот. Процесс утоньшения эффективен не всегда, а при использовании некоторых алгоритмов выделения признаков, таких как образное наложение, вообще невозможен. При использовании же сегментирующих алгоритмов необходим. Процедуру утоньшения необходимо проводить под строжайшим контролем.

Под утоньшением будем понимать преобразование изображения, удовлетворяющее следующим условиям: после преобразования все линии имеют толщину в один элемент; преобразование не нарушает топологию символа, т. е. линиям и узлам исходного изображения соответствуют линии и узлы в преобразованном изображении; преобразование не нарушает основных размеров символа. Предложенный метод утоньшения обладает тем преимуществом, что он ориентирован на построчную обработку растра, а это увеличивает его быстродействие [1].

Рассмотрим три последовательные строки растра (i-1)-ю, i-ю и (i+1)-ю. Выделим в i-ой строке произвольный элемент, который обозначим через  $\alpha$ . Этот элемент имеет в выбранных строках восемь соседних элементов, которые обозначим как элементы двумерного массива:

| j-1               | J               | j+1               |

|-------------------|-----------------|-------------------|

|                   |                 |                   |

| $\alpha(i-1,j-1)$ | $\alpha(i-1,j)$ | $\alpha(i-1,j+1)$ |

| α(i,j-1)          | α               | $\alpha(i,j+1)$   |

| $\alpha(i+1,j-1)$ | $\alpha(i+1,j)$ | $\alpha(i+1,j+1)$ |

| i-1 |  |

|-----|--|

| i   |  |

| i+1 |  |

Основная идея процедуры утоньшения заключается в том, чтобы отыскать на изображении крайние сверху, снизу, справа и слева элементы, а затем вынести решение о возможности их удаления с соблюдением перечисленных выше условий. Естественно, элемент  $\alpha$  считать крайним сверху, если он и элемент  $\alpha(i+1,j)$  зачернены, а элемент  $\alpha(i-1,j)$  незачернен. Формально эту ситуацию можно выразить так: элемент является крайним сверху, если равна единице следующая булева функция, в которой символы переменных совпадают с номерами элементов:

$$\varphi_{B} = \overline{\alpha(i-1,j)} \wedge \alpha(i+1,j) \wedge \alpha$$

Далее, если данный элемент  $\alpha$  является крайним сверху, то будем придавать ему значение 0 (будем стирать этот элемент), если равна единице следующая функция:

$$f_{B} = \overline{\alpha(i\text{-}1,j\text{+}1)} \wedge \alpha(i,j\text{-}1) \vee \overline{\alpha(i\text{-}1,j\text{-}1)} \wedge \alpha(i,j\text{+}1) \vee \alpha(i,j\text{+}1) \wedge \alpha(i,j\text{-}1).$$

Таким образом, элементу  $\alpha$  будет придаваться нулевое значение при равенстве единице следующей функции:

$$g_B = \phi_B \wedge f_B = \overline{\alpha(i\text{-}1,j)} \wedge \alpha(i\text{+}1,j) \wedge \alpha(\alpha(i\text{-}1,j\text{+}1) \wedge \alpha(i,j\text{-}1) \vee \alpha(i\text{-}1,j\text{-}1) \wedge \alpha(i,j\text{+}1) \vee \alpha(i,j\text{+}1) \wedge \alpha(i,j\text{-}1))$$

Элемент растра является крайним слева, если равна единице функция  $\phi \pi = \overline{\alpha(i,j-1)} \wedge \underline{\alpha(i,j+1)} \wedge \alpha$ . Этот элемент подлежит стиранию, если функция  $f \pi = \overline{\alpha(i-1,j-1)} \wedge \alpha(i+1,j) \vee \underline{\alpha(i+1,j-1)} \wedge \alpha(i-1,j) \vee \alpha(i+1,j)$  равна единице.

Следовательно, gл =  $\overline{\alpha(i,j-1)} \wedge \alpha(i,j+1) \wedge \alpha(\overline{\alpha(i-1,j-1)} \wedge \alpha(i+1,j) \vee \overline{\alpha(i+1,j-1)} \wedge \alpha(i-1,j) \vee \alpha(i-1,j) \wedge \alpha(i+1,j)).$

Рассуждая таким же образом, получим gн и gп, определяющие подлежащие стиранию крайние нижние и крайние правые элементы растра:

$$\begin{aligned} & \text{gh} = \overline{\alpha(i+1,j)} \wedge \alpha(i-1,j) \wedge \alpha(\underbrace{\alpha(i+1,j-1)} \wedge \alpha(i,j+1) \vee \underbrace{\alpha(i+1,j+1)} \wedge \alpha(i,j-1) \vee \alpha(i,j-1) \wedge \alpha(i,j+1)). \\ & \text{gn} = \overline{\alpha(i,j+1)} \wedge \alpha(i,j-1) \wedge \alpha(\underbrace{\alpha(i+1,j+1)} \wedge \alpha(i-1,j) \vee \underbrace{\alpha(i-1,j+1)} \wedge \alpha(i+1,j) \vee \alpha(i+1,j) \wedge \alpha(i-1,j)). \end{aligned}$$

Процедура утоньшения состоит в последовательном преобразовании исходного символа на растре в новый символ путем стирания сначала крайних сверху, затем крайних слева, далее крайних снизу и справа элементов. Этот цикл можно повторять до тех пор, пока на некотором цикле ни одна из функций не обратится в единицу. Но ввиду не замкнутости большинства символов это приведет к нежелательному стиранию некоторых элементов. Реализация алгоритма на ЭВМ показала, что для утоньшения требуется не более lmax/2 циклов, где lmax — максимальная толщина линии в исходном символе. Отметим, что порядок стираний может быть и иным, например, можно начать со стирания крайних правых элементов, затем крайних левых и т. д. Если  $\alpha$  — i -я строка исходного символа на растре  $\alpha$ в,  $\alpha$ л,  $\alpha$ н и  $\alpha$ п — i -я строка символа, полученного стиранием соответственно верхних, крайних левых, нижних и правых элементов, то можно записать

$\alpha B = \alpha \oplus g B$   $\alpha \pi = \alpha \oplus g \pi$   $\alpha H = \alpha \oplus g H$   $\alpha \Pi = \alpha \oplus g \Pi$

Здесь символ ⊕ обозначает операцию сложения по модулю 2.

Как уже отмечалось, процедуры утоньшения могут привести к изменению топологии символа, если внутри линий будут пустоты. Поэтому процесс заполнения пустот целесообразно предпослать утоньшению и стиранию бахромы. Как показали эксперименты, хорошие результаты при заполнении пустот дает следующее преобразование символа: элемент  $\alpha$  полагается равным единице, если равны единице пять из восьми соседних с ним элементов.

На рис. 1 показаны отдельные символы, введенные с помощью сканера, и результаты работы описанной предобработки. Как видно, результаты удовлетворяют поставленным требованиям.

Рис. 1 Результат описанной предобработки

В результате обработки описанными выше алгоритмами, к сожалению, не всегда получаем сегментированный символ, дальнейшая сегментация производится в процессе выделения признаков и распознавания.

#### Литература

- 1. Купчинаус С.В. «Алгоритм утоньшения изображений» межвузовский сб. дискретные системы обработки информации, вып 2 Ижевск: Ижевск. Мех.институт. 1979, с 23-27

- 2. Губерман Ш.А. Розенцвейг В.В. «Алгоритм распознавания рукописных текстов» // Автоматика и телемеханика, 1976, №5

- 3. Сунь Ц.Ю., Берто М., Мори С. «Автоматическое распознавание рукописных символов» ТИИРЭ, т.68, №4, 1980, с. 44-65

- 4. Фор А. «Восприятие и распознавание образов» /Пер. с фр./-М.: Машиностроение, 1989, 272 с.

- 5. Виттих В.А., Сойфер В.А. «Обработка изображений в автоматизированных системах научных исследований» М.: Наука, 1982, 216с.

# ИМПЕРИЯ СЧИСЛЕНИЙ А. Ю. ПОТЁМКИН МГТУ ИМ.Н.Э.БАУМАНА

## КАФЕДРА ИУ4 «КОНСТРУИРОВАНИЕ И ТЕХНОЛОГИЯ ПРОИЗВОДСТВА ЭВ И ТС»

## **EMPIRE of CALCULATIONS**

**A.Potemkin** BMSTU, IU4

**Аннотация:** В работе рассмотрены математические модели, алгоритмы и программная реализация системы проведения вычислений произвольной размерности.

**The summary:** In activity the mathematical models, algorithms and programmatic implementation of a system of realization of calculuss of arbitrary dimension are reviewed.

#### ВЕДЕНИЕ

Вот уже на протяжении двух с половиной лет года я пишу свою программу, каждый день уделяя этому по несколько часов и отдавая всё своё свободное время. И вот, наконец, настало время, чтобы другие люди оценили мой труд.

Представляю проект "Империя Счислений", написанный под платформу Wintelx32 (8686) для операционной системы Windows 98. В своём далёком прошлом программа имеет своего предшественника — версию под DOS, которая уже презентовалась на районной конференции восточного округа Москвы и заняла место лауреата. В то время программа имела примитивный интерфейс, но сейчас проект презентуется с в несколько раз усовершенствованной внутренней и внешней структурой. Продукт занял 9 место на третьей межрегиональной всероссийской международной межотраслевой научной олимпиаде «Шаг в будущее, Москва», проходящей в МГТУ имени Баумана среди исследователей в области информационных технологий Москвы и Московской области.

С восьми лет я учился программировать на компьютере, а потом решил собрать все знания воедино и посвятить несколько лет своей жизни разработке программного проекта Империя Счислений. Но и на сегодняшний день далеко нельзя сказать, что я закончил свой проект. Настоящая же программа – логически завершенная бета версия будущего продукта. Я вложил в свою программу все силы и работал как днём, так и ночью.

#### 2 Используемые Средства

Я использовал язык, который считаю самым лучшим, высокопрофессиональным и оптимальным — Visual C++ 6.0 (Microsoft Visual C++ Enterprise Edition 6.0 Service Pack 3). При разработке использовались новые возможности современных технологий AppWizard, ClassWizard, ActiveX, MFC, COM, OLE, API, ALT, SEH, MRU.

#### 3 Поставленные цели

Изначально меня привлекали идеи программы не с красивыми картинками, а со сложной внутренней логической структурой. И я решился написать программный проект, дающий возможность выполнять такие вычислительные операции, которые очень нужны в науке и жизни с одной стороны и не выполняются никакой другой программой во всём мире (во всяком случае, никто не знает таких программ, MatLab на это не способна) с другой стороны. И вот Империя Счислений – это программа, способная выполнять вычислительные операции над числами неограниченной длины, произвольного экспоненциального показателя, как классические: сложение, вычитание, умножение, деление... так и очень даже изощрённые: поразрядное дополнение до единицы, точное дополнение до двух, противоположенное преобразование, экспоненциальное наложение и преобразование... а

главное – конвертация любого числа из любой системы счисления в любую другую. Здесь не накладывается никаких ограничений ни на размер числа, ни на его экспоненциальный показатель (позицию плавающей запятой), ни на фактический и формальный знак, ну разве только система счисления числа не может превышать 1d+5000. Если назвать Империю Счислений калькулятором, то для неё не существует такого понятия "разрядность", потому что она бесконечна.

Также Империя Счислений может выполнять дополнительные операции над числами, упрощающими и ускоряющими задание исходных чисел, например, упрощение числа, ввод числа в экспоненциальной форме, обращение фактического знака числа...

#### 4 Проблемы

У операционной системы Windows x32 максимальная разрядность вычислительных целочисленных операций — 64 бита, а с плавающей запятой — 80 бит, очевидно, что это накладывает большие ограничения на размеры чисел, следовательно, если речь идёт о числах, экспоненциальные показатели которых превышают 19, то здесь уже операционная система даёт приблизительный результат вычислений.

#### 5 Проектирование Алгоритма

В отличие от операционной системы Империя Счислений действует по другому принципу: имитируя вычисления, она содержит в себе два драйвера — drive\_strings и drive\_values, позволяющих производить вычисления с числами неограниченных размеров. Драйвер drive\_strings отвечает за хранение чисел в оперативной памяти, но ведь число может не уместится в ней, в этом случае драйвер кэширует дисковое пространство для числа и управляет вводом — выводом, используя какую — то часть памяти, тогда число может быть гигабайтного размера. Логическое распознавание числа, хранимого вышеописанным драйвером, производит драйвер drive\_values, способный имитировать все вычисления и представлять их через 3 элементарные операции — сложение, вычитание и умножение двух цифр. Таким образом, любой файл, также как любая последовательность символов может быть рассмотрен, как число, если конечно известна его система счисления и значение каждой цифры.

Никакие ранее созданные алгоритмы конвертации чисел не устроили меня, и мне пришлось создать новый алгоритм, универсальный для всех систем счисления, для любых экспоненциальных показателей чисел и знаков. Разработка его стоила мне большого труда. Старые бета — версии программы работали по другим, менее оптимальным, алгоритмам, также разработанным мною. Настоящий же алгоритм я назвал "Экспонентальным" (производится через экспонентальный логарифм). При разработке очень много времени было уделено оптимизации программного кода, в частности алгоритм программы специально рассчитан под процессоры корпорации Intel с технологией Рго, введена система буферизации ввода — вывода данных на диск...

Описать алгоритм Империи Счислений здесь совершенно не реально, ведь тысячи и тысячи строк исходного кода, составляющие её, не уместились бы даже в сотни листов печатного текста. Скажу лишь общий принцип "Экспонентального" алгоритма программы (он активизируется на этапе непосредственной конвертации, описанном ниже). Сначала вычисляется экспоненциальное приближение числа (дающее возможность оценить его далее просчитывается простое приближение, затем снова вычисляется экспоненциальное приближение, но уже с большей точностью, и таким образом, когда более точное приближение не отличается от последнего приближения, получается результат. В процессе вычислений работает очень большое количество функций, поочерёдно передающих друг другу управление, максимальная степень вложенности превышает десять вызовов функций. При разработке алгоритма программы широко использовались рекурсия, инвариантность, виртуальность, полиморфизм, абстрагирование, инкапсуляция,

контейнерность, дружественность, итераторность и другие возможности объектно – ориентированного программирования.

Империя Счислений интегрирует в себе 2 алгоритма конвертации — это описанный выше алгоритм, имитирующий все вычислительные операции с использованием драйверов drive\_strings и drive\_values, и алгоритм, с использованием возможностей операционной системы и с ограничением на размеры чисел. Алгоритм вычислений можно выбрать в опциях программы или указать в ini — файле.

#### 6 Практическое Применение

С первого взгляда кажется, что конвертация чисел мало где может использоваться, но это далеко не так. В недалёкой перспективе я запланировал программный проект "Империя Архиваций", который, унаследовав возможности "Империи Счислений", будет архивировать файлы с помощью конвертации. Алгоритм прост — переконвертировать заданный файл из его текущей системы счисления (определяющейся по количеству вариаций встречающихся в файле символов) в 256 — ричную систему счисления, и размер файла значительно сократится. Также с помощью конвертации чисел можно легко и совершенно нераспознаваемо шифровать информацию. Ведь любая последовательность символов, изменившая свою систему счисления хотя бы на единицу, становится неузнаваемой.

#### 7 Интерфейс

В итоге я создал две веши – это вычислительный алгоритм для конвертации чисел и полноценное Windows – приложение, способное обрабатывать все сообщения, имеющее удобный интерфейс, предоставляющее много сервиса.

Я не буду детально описывать интерфейс моей программы, подробную документацию Вы найдёте в справочной системе в комплекте продукта. Изложу лишь только основные положения. Империя Счислений имеет 21 диалоговых окон (без учёта стандартных окон), обеспечивающих сервис и многофункциональность программы, причём меню главного окна состоит из более 150 пунктов. Среди этих окон — специализированные редакторы конвертируемого числа и счислительных цифр (о них ниже), бинарный редактор, опциональные окна, резидентные контролеры, мастера...

В качестве исходных параметров Империя Счислений предлагает ввести число для конвертации (либо файл, содержащий его), систему счисления этого числа, систему счисления, в которую его следует сконвертировать и счислительные цифры (последовательность цифр, определяющая значение каждой используемой цифры (в качестве стандарта предлагается: "0123456789ABCDEFGHIJKLMNOP

QRSTUVWXYZabcdefghijklmnopqrstuvwxyzБГДЁЖЗИЙЛПУФЦЧШЩЪЫЬЭЮЯбвгдёжзийк лмнптфцчшщъыьэюя")).

Счислительные цифры позволяет ввести специализированный редактор и бинарный редактор.

Процесс конвертации делится на четыре этапа: инициализация, генерация объектного кода, конвертация и финальные операции. На инициализации производится распознавание числа: определяется позиция запятой, считывается информация о знаке и создаётся объектный код, специфический для системы счисления конвертируемого числа, описывающий его, для дальнейших процессов вычислений. На этапе генерации временного объектного кода генерируется другой код на основе уже созданного кода, дающий исчерпывающую информацию о числе, универсальную для всех систем счисления и необходимую для непосредственной конвертации. На конвертации из объектного кода конвертируемого числа создаётся объектный код результата конвертации, этот процесс, как правило, самый долговременный и сложный. На этапе финальных операций производятся экспоненциальные счисления, если это указано в опциях (вычисляются дополнительные научные сведения о результате операций, например, научная нотация), высчитывается противоположенное преобразование (также в зависимости от опций) и из объектного кода

результата конвертации генерируется сам результат. Информацию в реальном времени о процессах конвертации и их процентах выдаёт специализированный "резидентный модуль", также показывающий время, затраченное на операции, и количество вычислительных тактов, проведённых для получения результата.

По окончанию конвертационно — вычислительных операций выводится имя файла, содержащего результат, или сам результат (в зависимости от настроек), который можно просмотреть, как в текстовом, так и в бинарном формате (используя бинарный мастер). Бинарный мастер выводит результат операций, как последовательность кодов в 2, 8, 10, 16 и 256 — ричных системах счисления, где каждый код представляет собой цифру. Вы можете сохранить файл, связанный с результатом вычислений, сохранить его под выбранным именем или же определить этот файл, как временный, тогда он автоматически удалится по окончанию работы программы. Система межмодульного обмена, интегрированная в Империю Счислений, позволяет просмотреть этот файл внешними редакторами. Также предоставляется возможность получить дополнительную научную информацию о результате конвертации, в частности научную экспоненциальную нотацию в системе счисления результата и противоположенное преобразование, которое так же можно сохранить.

#### 8 Обработка Исключений

Империя Счислений интегрирует в себе "резидентный обработчик исключений", который в реальном времени контролирует корректность вычислительных операций, и в случае ошибки или при возникновении исключительной ситуации обработчик останавливает процесс вычислений, выдаёт соответствующее сообщение и предоставляет возможность пользователю выбрать выход из ситуации: обработка исключения, игнорирование, игнорирование всех ошибок, перезапуск приложения, выход из программы, терминирование программного кода, установка настроек по умолчанию, остановка. Кроме того есть дополнительно 3 обработчика ошибок, которые вызываются в зависимости от фатальности исключений. Обрабатываются ошибки по технологии SEH с использованием глобальной раскрутки стека вызовов.

#### **9 SDI Концепции**

Программа является SDI – приложением, при инсталляции мастер установки регистрирует тип файлов "eoc" (от английского названия "Empire Of Calculations") как "Числа Империи Счислений". Поддержаны почти все стандартные операции над файлами, такие как создание, открытие, загрузка и сохранение файлов. Во время работы программы открыто 15 файлов – это файл, связанный с исходным числом (в нём всегда содержится заданное число для конвертации), файл, связанный с вторичным аргументом (для бинарных связанный с результатом операций, файл противоположенного операций), файл, преобразования и файл объектного кода, а также 10 файлов – кэш буферов вычислительного драйвера. Империя Счислений предоставляет возможность межмодульного обмена между приложениями DOS и Windows, например, можно редактировать число для конвертации или просмотреть результаты операций внешними редакторами (Блокнот, WordPad, Word, Norton commander...). Впрочем, программа имеет встроенные редакторы конвертируемого числа, мастер технических подробностей, бинарный мастер просмотра результата... Открыть файл Империей Счислений можно также, щелкнув два раза мышкой по файлу "еос", после инсталляции или выбрав Империю Счислений в окне "Открыть с помощью" операционной системы, или через командную строку, или через запрос на открытие от другой программы, либо воспользовавшись меню отправить.

Бинарный редактор, например, позволяет ввести каждую цифру конвертируемого числа, как код в 2, 8, 10, 16 и 256 — ричной системе счисления. Таким образом, Империя Счислений также является текстовым и бинарным редактором файлов.

#### 10 Возможности Настройки

Империя Счислений имеет много возможностей настройки, которые записываются в системный реестр и ini — файл, в частности можно отключить поддержку плавающей запятой, отрицательных чисел, резидентный обработчик исключений, резидентный модуль, визуальное анимирование, задать размер оперативной памяти, буферизируемой для вычислений и путь дискового пространства для кэширования, можно отрегулировать приоритет вычислительного процесса, указать его скорость... Автоматически создаётся список последних открытых файлов по технологии MRU, позволяющий быстро перейти к недавно использованному файлу.

#### 11 Справочная система

В комплекте продукта состоит справочная система со встроенным мастером поиска, содержанием, указателем, контекстной справкой, советами дня и справкой о пользовании справкой. Нажав правую кнопку мышки на любом элементе Империи Счислений, пользователь немедленно получает соответствующую краткую информацию, а при нажатии F1 выдаётся справка об активном элементе. Режим ознакомления программы помогает начинающим пользователям, выдавая информации обо всех элементах по которым был произведён щелчок мышью.

#### 12 Инсталляционная утилита

Инсталлирует программу специальный мастер установки, позволяющий выбрать тип установки, комплект, директорию назначения или место в локальной сети и соответственно перенастроить системный реестр, рабочий стол и меню "Пуск" пользователя. Полный комплект установки составляет 7 мегабайт. Деинсталлировать продукт можно через приложение "Установка и удаление программ" на панели управления или ярлык в меню "Пуск".

#### 13 Перспективы

В перспективе Империя Счислений будет уметь совершать арифметические операции с числами любых размеров и систем счисления, например, извлечение логарифма с основанием в любой системе счисления из числа любой системы счисления. В итоге я хочу сделать Империю Счислений уникальной вычислительной машиной.

#### 14 Это Интересно...

Проект Империя Счислений разрабатывался два с половиной года и, по – видимому, будет разрабатываться ещё дольше. В это сложно поверить, но порой месяцами каждый день я в среднем уделяю программированию 4 – 5 часов, что практически составляет всё моё свободное время. Объектно – ориентированная структура программы содержит 27 классов (исключая классы МГС) и более 1000 объектов (очень сложно было бы сосчитать), включая функции (исключая библиотечные объекты и функции АРІ). Директория с исходными кодами моего проекта занимает около 50 мегабайт памяти и содержит 816 файлов (без учёта предопределённых библиотек), среди них 28 файлов типа "срр" и 30 библиотек "h", а самый главный "срр" файл программы инкапсулирует более 150 экранов текста (150000 знаков или 114 страниц А4 14 шрифтом). Исходные кода Империи Счислений лишь только в простом неформатированном текстовом формате занимают около 800 Кб. Причём все эти величины со временем динамически растут.

#### 15 Заключение

...Но всё – таки все возможности Империи Счислений можно узнать лишь только методом полной практической индукции.

### ВИРТУАЛЬНЫЙ МУЗЕЙ «ИСТОРИЯ РАЗВИТИЯ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ» Колосков Дмитрий Владимирович

Научный руководитель: профессор, д.т.н. Белов Б.И. Физико-математического лицея №1580 при МГТУ им. Н.Э.Баумана koloskov@iu4.bmstu.ru

## VIRTUAL MUSEUM "A HISTORY OF DEVELOPMENT OF COMPUTER FACILITIES"

Koloskov D.V.

The scientific chief: the professor, Dr. Belov B.I.

Physical and mathematical Liceum №1580 at BMSTU koloskov@iu4.bmstu.ru

Аннотация: В работе рассмотрены инструментальные средства, технологии и методика создания и администрирования информационно - справочной интернет системы по истории вычислительной техники, раздел "От Абака до компьютера".

The summary: In activity the tools are reviewed, technologies both the technique of creation and management by orders and decrees is informational - reference Internet of a system on a history of computer facilities, section " From an Abacus up to the computer ".

#### Введение

За последние несколько лет в российском интернете появилось огромное количество школьных страничек, информационно-образовательных и развлекательных порталов, научных, технических проектов и просто домашних страничек, сделанных руками школьников.

Сегодня каждый из нас работает за высокопроизводительными компьютерами, часто объединенными в локальные сети и имеющие выход в интернет. Мы используем современные принтеры, сканеры, плоттеры, модемы и многие другие цифровые устройства — последние достижения науки и техники. Однако, мы не часто задумываемся об истории и развитии вычислительной техники, их создателях, в чьих умах рождались гениальные идеи построения вычислительных машин, облегчивших бы рутинный труд человека, помогшей бы многим ученым сделать следующий шаг в их деятельности.

#### Обзор проектов по виртуальным компьютерным музеям

Одно из направлений развития музейных экспозиций в Internet — появление виртуальных музеев информатики и вычислительной техники. Реально эти музеи могут и не существовать, однако их виртуальные экспозиции насчитывают многие экспонаты, фотографии и биографии известных людей.

Во многих странах Европы, США, Канады, Австралии существуют компьютерные музеи, как реальные, так и виртуальные. В них можно найти информацию, как и о первых вычислительных машинах, так и о современных технологиях. На их web сайтах можно подробно узнать о биографии ученых, выдающихся разработчиков и программистов, президентов крупнейших компьютерных компаний, сведения по архитектуре того или иного компьютера. Большинство музеев предлагают информацию на английском языке.

Интерес к виртуальным музеям постоянно растет и поэтому посещаемость сайтов увеличивается также быстро. Так, например, web сайт, содержащий каталог компьютерных музеев и выставок — The Virtual Museum of Computing (VMoC) (<a href="http://nic.icom.org/vlmp/computing.html">http://nic.icom.org/vlmp/computing.html</a>) посещают ежедневно более трехсот человек.

Один из самых популярных сайтов, посвященных развитию вычислительной техники — это сайт калифорнийского колледжа (<u>http://www.computer-museum.org/</u>), который содержит богатую экспозицию как "настоящих", так и виртуальных экспонатов.

Также популярны музеи, посвященные выдающимся личностям, внесшие большой вклад в развитие вычислительных технологий.

На европейских серверах есть музеи, посвященные Чарльзу Бэббиджу (<a href="http://www.comlab.ox.ac.uk/oucl/users/jonathan.bowen/babbage.html">http://www.comlab.ox.ac.uk/oucl/users/jonathan.bowen/babbage.html</a>), Аде Лавлейс (<a href="http://www.cs.yale.edu/homes/tap/ada-lovelace.html">http://www.cs.yale.edu/homes/tap/ada-lovelace.html</a>).

Среди виртуальных компьютерных музеев рунета крупнейшим является — "Компьютерный виртуальный музей" РС Week/RE ( <a href="http://www.computer-museum.ru">http://www.computer-museum.ru</a> ). Посещая его страницы создается впечатление, что здесь можно найти абсолютно все: история развития ВТ, программного обеспечения, вычиления в докомпьютерную эпоху.

#### Проект "История вычислительной техники"

Представленная мною работа носит название "История вычислительной техники" и размещена по адресу (<a href="http://museum.iu4.bmstu.ru">http://museum.iu4.bmstu.ru</a>) — на web сервере кафедры «Конструирование и производство электронной аппаратуры» МГТУ им. Н.Э.Баумана, занимающейся непосредственно разработкой и созданием ЭВМ с 1938 года. Цель создания виртуального музея — появление русскоязычного ресурса, в котором бы удалось сконцентрировать те необходимые сведения, которые нужны любому ученику, учителю информатики, желающим познакомиться с интересующей их информацией о развитии вычислительной техники в прошлом и современных информационных технологиях.

В проекте «История развития вычислительной техники» была сделана попытка по шагам проследить развитие вычислительной техники начиная от абака — дощечки покрытой слоем пыли, на которой острой палочкой проводились линии и какие-нибудь предметы, размещавшиеся в полученных колонках по позиционному принципу, и заканчивая современными микропроцессорами, компьютерами и серверными платформами.

Рис.1 Web-сайт виртуального музея истории вычислительной техники

На страницах виртуального музея можно найти фотографии и описания арифметической машины Паскаля (Паскалево колесо), арифмометра Полени, машины

Бэббиджа, вычислителя Лейбница, созданных с небольшим промежутком времени с середины XVII века.

Очень интересен раздел, посвященный программируемой механической вычислительной машине Чарльза Бэббиджа. Начиная с 1812 года Ч. Беббидж работал над изготовлением механической вычислительной машины более 30 лет. "Элементной базой" машины Беббиджа служили "цифровые" колеса с различным числом зубьев. Созданная в 1834 году Чарльзом Бэббиджем аналитическая машина стала первым прообразом современных компьютеров.

Рис.2. Абак

Рис.3. Узелки

Большое внимание уделено ЭВМ, созданным в середине XX века. Первая ЭВМ – "Эниак" была создана в США в 1948 году. Она была очень специализирована и выполняла ограниченное число задач. Первые отечественные ЭВМ данного поколения были созданы немного позднее. К ним относятся таким ЭВМ, как "БЭСМ-1", "Урал-1" и др.

Бурное развитие полупроводниковой технологии позволило в начале 70-х годов перейти к созданию больших и сверхбольших интегральных схем (БИС И СБИС), на основе которых были созданы ЭВМ, производящие десятки миллионов операций в секунду. Одними из самых мощных ЭВМ данного поколения являются ЭВМ семейства "Крейт" (США) и "Эльбрус" (Россия), которые являются многопроцессорными системами и содержат до нескольких миллиардов транзисторов.

Говоря о развитии вычислительной техники нельзя не сказать о программном обеспечении, без которого любой компьютер – просто кусок железо. Начиная с 60-ых годов особое внимание уделяется разработкам программного обеспечения. Появились языки программирования: Fortran, LISP, LOGO, Pascal. Разработана операционная система UNIX. Возникает потребность объединения отдельных компьютеров в сеть. В разделе "Персонали" отмечены ученые, внесшие наибольшие вклад в создание и развитие вычислительной техники. Среди них Джон Буль, Чарльз Бэббидж, Норберт Винер, Джон Фон Нэйман, Лавлейс Ада Аугуста, Готфрид Вильгельм Лейбниц, наши соотечественники: Сергей Алексевич Лебедев, Алексей Андреевич Ляпунов, наши современники: Питер Нортон, Билл Гейтс, Дмитрий Лозинский.

Последняя экспозиция виртуального музея – современные достижения компьютерных технологий – разработки конца 90-х годов, представлены разделы по CISC и RISC архитектурам микропроцессоров.

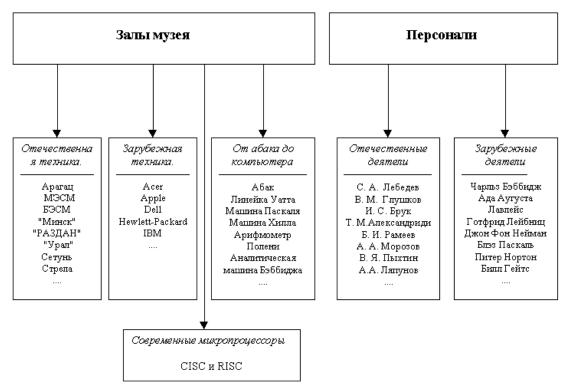

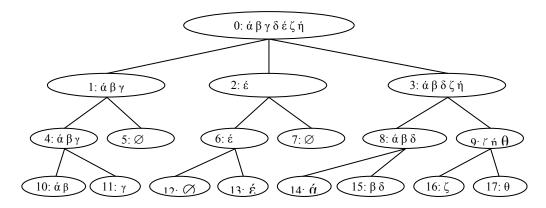

Сайт имеет простой, спокойный дизайн с удобной продуманной навигацией по структурной схеме типа «дерево». Имеющиеся виртуальные экспозиции разбиты на разделы: залы музея и персонали. На сегодняшний день разработаны четыре зала музея: отечественная техника, зарубежная техника, от абака до компьютера, CISC и RISC архитектуры микропроцессоров. Есть навигационное меню, помогающее ориентироваться по хронологической последовательности развития ЭВМ, приведены ссылки на другие виртуальные музеи мира по информационным технологиям.

Рис.4. Структурная схема построения виртуального музея.

Рис. 5. Страница музея, посвященная С.А. Лебедеву

#### Технические средства реализации проекта

Для создания информационного сетевого ресурса, отвечающего требованиям стильного оформления и высоким качеством визуального восприятия, были использованы современные средства разработки и пакеты программного обеспечения ведущих мировых разработчиков, применяемые в профессиональном дизайне, обработке машинной графики и

разработки — HTML версии 4.0 с применением элементов Dynamic HTML. Активные элементы, используемые при реализации проекта были написаны с использованием Java Script, удобным инструментарием создания единых стилистических подходов во всех страницах были таблицы стилей CSS. При разработке графических изображений основным инструментарием был Adobe Photoschop 5.5, также использована CorelXara. Анимационная часть проекта написана при помощи Ulead Gif Animator. Для создания большинства

Рис. 6. Раздел по CISC и RISC архитектурам микропроцессоров

#### Заключение

Проект "История развития вычислительной техники" ещё достаточно молод. При создании этого web ресурса мною овладевало стремление и интерес заглянуть в прошлое, узнать как мыслили и рассуждали создатели всем известных машин МЭСМ, БЭСМ, Урал, ENIAC. Виртуальной экспозиции положено фундаментальное начало и с появлением новой техники, ростом информационных технологий его ждет, без сомнений, пополнение новых виртуальных экспозиций и интересное развитие.

# ЛАБОРАТОРНАЯ УСТАНОВКА ПО КУРСУ ФИЗИКИ РАЗДЕЛ: ТЕОРИЯ КОЛЕБАНИЙ

#### Купавцев Алексей Владимирович

Научный руководитель: к.т.н., доцент Власов А.И.

Средняя общеобразовательная школа №906 alexkup@newmail.ru.

# THE LABORATORY INSTALLATION AT THE RATE OF PHYSICS SECTION: A VIBRATION THEORY

Kupavcev A.V.

The scientific chief: Ph.D., senior lecturer Vlasov A.I.

Mean comprehensive school №906

alexkup@newmail.ru

**Аннотация:** В работе рассматривается разработка и эксплуатация лабораторной установки по курсу физика - раздел "Теория колебаний". В основу установки положены методы активного управления волновыми полями, в качестве средств цифровой обработки сигналов использована звуковая плата ПЭВМ, в качестве регистрирующей аппаратуры - микрофоны, излучателей колебаний - динамики.

**The summary:** In activity the mining and exploitation of the laboratory installation at the rate physics - section "Vibration theory" is esteemed. The methods of fissile control of wave fields are trusted to in the basis of the installation, as means of a digital signal processing the PC sound card utilised, as a recording equipment - microphones, radiators of oscillations - dynamics.

#### Введение

Активное управление волновыми полями — одно из бурно развивающихся сегодня направлений прикладной науки и техники. Методы изучения волновых процессов доведены физиками до совершенства, однако, задачи управления ходом этих процессов не имеют общего решения.

Среди наиболее наглядных примеров решения задач этого класса — созданные в последние годы средства защиты от вредного воздействия акустических шумов.

Большинство используемых сегодня методов защиты от шума реализованы пассивными средствами. При гашении низкочастотных колебаний такие средства малоэффективны, а их объемы и масса недопустимо возрастают. Приходится разрабатывать все новые и новые средства защиты людей, работающих с современной техникой. Все чаще требуются такие средства защиты, которые могут адаптироваться к изменяющимся условиям среды. Именно здесь и находят применение активные средства защиты, в которых используются дополнительные источники энергии.

Такие системы (САГ) формируют с помощью компенсирующих излучателей дополнительное гасящее поле с требуемыми пространственными и частотными характеристиками.

Но развитие САГ дальше невозможно без новых специалистов, а для этого надо их подготовить. Как показывает опыт, наибольший эффект в обучении дают программные системы, сочетающие в себе элементы тестирования и активного обучения. Методология применения таких систем заключается в разбиении учебного процесса на три этапа: экспериментальное исследование объекта в реальном масштабе времени, математическое моделирование и защита отчета с использованием контрольно-обучающей подсистемы. В ней пользователь получает возможность пройти обучение в сочетании с контролем полученных знаний по различным разделам теории проектирования САГ и смежных с ней дисциплин. Системы активного гашения как нельзя лучше подходят для того, чтобы на

области конкретных примерах показать достаточно серьезные приложения микропроцессорных систем и дать школьнику поэкспериментировать с ними.

1. Разработка проекта "Лабораторная установка по курсу физики, раздел: теория колебаний".

#### Техническая реализация проекта.

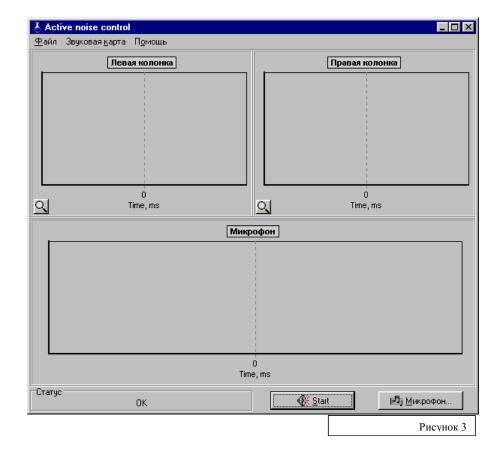

Целью данной работы было создание программы для моделирования принципов активного управления акустическими полями, применительно для лабораторных работ по физики.

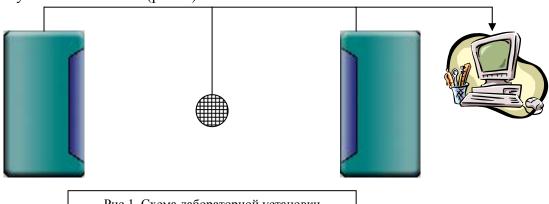

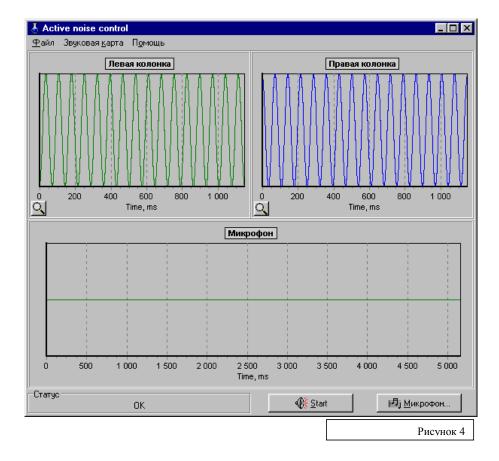

Предполагаемая лабораторная установка состоит из мультимедиа-компьютера (ПК + микрофон + динамики + звуковая плата) и программного обеспечения для генерации звуковых колебаний.(рис. 1)

Рис.1. Схема лабораторной установки

Такой состав лабораторной установки позволяет использовать ее при достаточно минимальных денежных затратах, например в школах. Ведь давно не секрет что школы испытывают нехватку средств на закупку лабораторных принадлежностей – а вот персональный компьютер на данный момент есть почти в каждой школе, остается только сделать его мультимедийным и все.

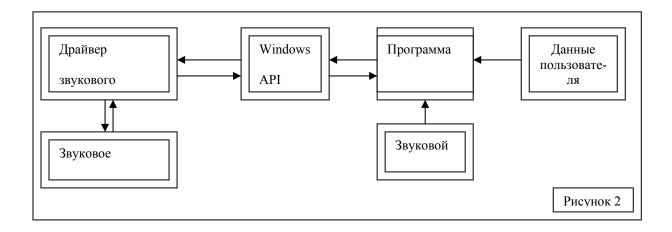

#### Программная реализация проекта.

Программа выполнена на Borland Delphi 5 с использованием стандартных библиотек Microsoft Windows 9.х. В связи с тем что библиотеки Microsoft не могут преобразовывать звуковую волну в обратную ей и не могут воспроизводить две разных звуковых волны в различных колонках, одновременно, пришлось воспользоваться более низкоуровневыми библиотеками Windows – на уровне DLL библиотек. В связи с этим приходилось считывать звуковой файл 'в ручную' то есть на уровне работы с файлом и далее анализировать данные в файле, для последующего проигрывания и построения спектра звуковой волны. Процедура считывания файла с звуковыми данными и построения графика волны представлена в листинге 1.

```

Листинг 1

procedure TForm1.N9Click(Sender: TObject);

var

f:file;

i.l.d:longint;

wavinfo:TPCMWaveFormat;

begin

{}

DATA ID:=mmioStringToFOURCC('data',0);

if opendialog1.Execute then filename:=opendialog1.FileName

```